# **DATA SHEET**

www.semefab.com

Over 500 million die shipped per year

# OPTICAL FRONT END ASIC SF107

# **BRIEF DESCRIPTION**

Designed specifically for the optical smoke detector market, the Semefab SF107 is a high performance, low cost, low noise and low power interface between an optical smoke detector chamber and a microprocessor. With an integrated low capacitance photodiode and low noise amplifiers, the SF107 is synchronised with the IR pulse to minimise noise and cancel offset.

### **FEATURES**

- Output voltage proportional to chamber smoke level

- 8 pin SOIC(N) with glass aperture.

- Supply voltage range 3.0 5.5V

- 10nA typical guiescent current

- 110μA typical active current

- 7V/μW/cm² photo sensitivity

- High rejection of ambient light

- Possibility to eliminate lenses from sensors due to the high signal to noise ratio

- Very low temperature coefficient over the operating temperature range

- Low impedance, high amplitude output removes the need for conformal coating or guard tracks on the PCB

- High immunity to impressed EMC

- Bias Voltage on output to improve accuracy of low smoke levels

# BLOCK DIAGRAM Vdd CS SAMPLE TEST photodiode Amp 1 Amp 3 AMP2\_OUT AMP3\_IN 1nF 1

Rev A Page 1 of 5

# DATA SHEET OPTICAL FRONT END ASIC REV A

www.semefab.com

Over 500 million die shipped per year

# **GENERAL DESCRIPTION**

The SF107 ASIC is manufactured using Semefab's OPTO-CMOS process. It is designed specifically to provide a robust, low power, and very easy to use interface between a microprocessor and the smoke chamber in an optical smoke detector sensor unit.

The ASIC contains a 1.0mm<sup>2</sup> PIN photodiode. The photodiode has low self-capacitance which allows a rapid response to light and assists the design of the low noise amplification and integration circuit.

The SF107 includes internal circuits to cancel ambient light, amplifier input offset voltage, and noise.

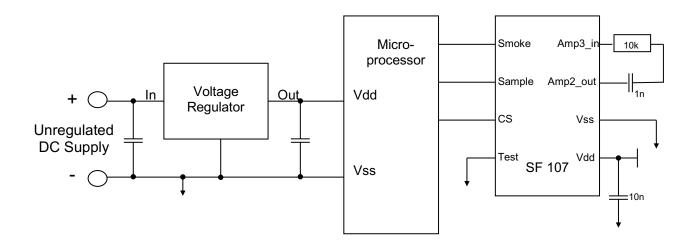

Only two control signals are required between the ASIC and the micro. Chip Select (CS) switches the chip between standby mode and active mode. When the CS input is logic 1, the chip is active. When the CS input is logic 0, the chip is held in low power quiescent state. A logic 1 at the SAMPLE input during the CS period enables the reading of a smoke sample. The SAMPLE time period must coincide with the switching of the IR LED into the smoke chamber. Depending on the application and the system current requirements, a typical timing cycle could be CS enabled for 10ms at 2-second intervals.

# PIN DESCRIPTION

| PIN | NAME     | FUNCTION                                                                                                                                                                                 |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | TEST     | This pin is allocated for testing. For normal use connect it to pin 2.                                                                                                                   |

| 2   | CS       | Control input from the micro. The device is active when CS is at logic                                                                                                                   |

| 3   | SAMPLE   | Control input from the micro. A positive pulse at this input initiates the smoke reading. The SAMPLE pulse should coincide with the pulse to the IR LED.                                 |

| 4   | SMOKEOUT | The analogue voltage representing the smoke reading appears at this pin after the back edge of SAMPLE. A sample and hold function holds the SMOKEOUT voltage to the end of the CS pulse. |

| 5   | AMP3_IN  | The input to the third amplifier. AMP2_OUT is connected externally to AMP3_IN via a 1N cap and a 10K resistor.                                                                           |

| 6   | AMP2_OUT | The output of the second amplifier.                                                                                                                                                      |

| 7   | VSS      | Negative input pin (GND). Common with the micro GND.                                                                                                                                     |

| 8   | VDD      | Positive power supply for the ASIC. The Vdd range is 3.0 to 5.5V. The SF107 would normally operate between the same supply rails as the microprocessor.                                  |

Rev A Page 2 of 5

# DATA SHEET OPTICAL FRONT END ASIC REV A

www.semefab.com

Over 500 million die shipped per year

# **DEVICE PARAMETERS**

| Parameter                                                           | Symbol | Min     | Typical | Max     | Unit                 |

|---------------------------------------------------------------------|--------|---------|---------|---------|----------------------|

|                                                                     |        |         |         |         |                      |

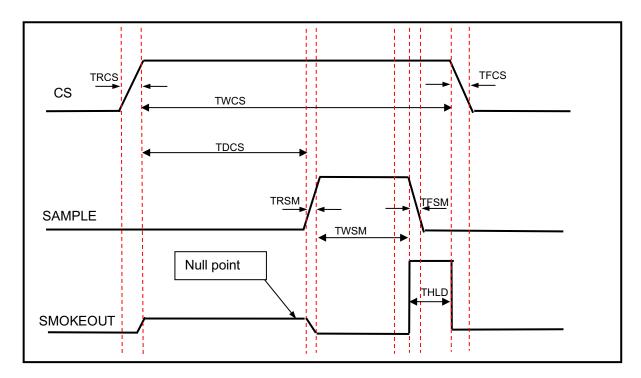

| Width of CS pulse                                                   | TWCS   | 4.5     | 10      |         | ms                   |

| Width of SAMPLE pulse                                               | TWSM   | 450     | 500     | 550     | μS                   |

| Rise time of CS (10% to 90%)                                        | TRCS   |         |         | 10      | μS                   |

| Fall time of CS (90% to 10%)                                        | TFCS   |         |         | 10      | μS                   |

| Rise time of SAMPLE (10% to 90%)                                    | TRSM   |         |         | 10      | μs                   |

| Fall time of SAMPLE                                                 | TFSM   |         |         | 10      | μS                   |

| Delay from leading edge of CS (90%) to leading edge of SAMPLE (10%) | TDCS   | 4.0     |         |         | ms                   |

| Hold time for falling edge of SAMPLE (10%) to falling edge of CS    | THLD   | 300     |         |         | μs                   |

| Operating voltage                                                   |        | 3.0     | 3.3     | 5.5     | Vdc                  |

| Operating temperature range                                         |        | -40     |         | +85     | ٥C                   |

| Standby current - Cs low                                            |        |         | 0.01    | 1.0     | μΑ                   |

| Operating current -Cs high                                          |        |         | 0.1     | 0.25    | mA                   |

| SMOKEOUT voltage swing from bias                                    |        |         |         | Vdd-0.3 | Vdc                  |

| SMOKEOUT bias voltage (dark) (Note1)                                |        | 0.05    | 0.15    | 0.25    | Vdc                  |

| Photo responsitivity (Note 2)                                       |        | 5.6     | 7       | 8.4     | V/μW/cm <sup>2</sup> |

| Noise equivalent power density                                      |        |         | 0.5     | 1       | nW/cm <sup>2</sup>   |

| Logic 1 level for CS and SAMPLE                                     |        | Vdd-0.4 |         | Vdd     | V                    |

| Logic 0 level for CS and SAMPLE                                     |        | GND     |         | 0.4     | V                    |

| Temp co. of SMOKEOUT voltage                                        |        |         | -2000   |         | ppm/ºC               |

| Change in responsivity with background light level of 0.06μW/cm²    |        | -10     |         | +10     | %                    |

Note 1. The ASIC design can be modified with a metal mask change to adjust the bias voltage.

Note 2. The ASIC design and layout permits other versions to be supplied with typical photo responsivity between 5 and  $50 V/\mu W/cm^2$

Rev A Page 3 of 5

www.semefab.com

Over 500 million die shipped per year

# **TIMING DIAGRAM**

CS and Sample are active high control signals from the micro.

# TYPICAL APPLICATION CIRCUIT

Rev A Page 4 of 5

# DATA SHEET OPTICAL FRONT END ASIC REV A

www.semefab.com

Over 500 million die shipped per year

# PRODUCT QUALIFICATION

|                                 | Conditions |                                                      |  |

|---------------------------------|------------|------------------------------------------------------|--|

| Moisture Sensitivity Level      | MSL3       |                                                      |  |

| High Temperature Operating Life | PASS       | Temp = 85°C<br>Vdd = 3.3V                            |  |

| High Temperature Storage        | PASS       | Temp = 125°C                                         |  |

| Temperature Humidity Bias       | PASS       | Temp = 85°C<br>Relative Humidity = 85%<br>Vdd = 3.3V |  |

### ORDERING INFORMATION

Order products using the following codes: SF107\_8 in an 8 pin SOIC IR (window) package

Preliminary datasheets contain specifications based on prototype analysis and are current on publication date. Semefab Ltd. may change this specification at any time without notification. Supply of products conforms to Semefab Ltd's Terms and Conditions

Semefab Ltd

Newark Road South

Eastfield Industrial Estate

Glenrothes, Fife KY7 4NS

Telephone: +44 (0) 1592 630 630

Fax: +44 (0) 1592 775 265

Email sales@semefab.co.uk

©Semefab 2004

Rev A Page 5 of 5